SmartSwitch™

## PC Card Current Limit Interface and Capacitor Charger

## **General Description**

The AAT4621 SmartSwitch is a current limited P-channel MOSFET power switch designed for high-side loadswitching applications in PC Card GSM/GPRS/3G modem cards. Used in conjunction with a super capacitor, the AAT4621 will ensure that the power ratings of the PCMCIA host are not exceeded at any time. Featuring two independent, programmable current limits and a power loop, the AAT4621 can ensure that the super capacitor can be charged without exceeding PCMCIA specifications. The current limit is set by two external resistors allowing a ±10% current limit accuracy over the normal operating temperature range. The switch can be controlled from either of the two enable inputs and in the off condition will block currents in both directions. The AAT4621 also incorporates a System READY function which can advise the system that the super capacitor is fully charged and ready for use. Adjustable hysteresis is provided with the addition of an external resistor. The quiescent supply current is typically a low 40µA. In shutdown mode, the supply current decreases to less than 1µA.

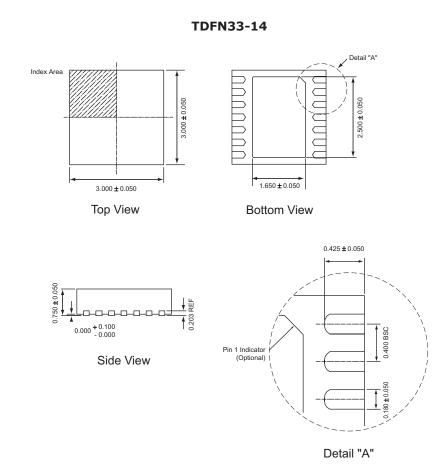

The AAT4621 is available in a thermally enhanced, Pb-free 14-pin TDFN33 package and is specified over the -40°C to 85°C temperature range.

## Features

- $V_{IN}$  Range: 3.0V to 5.5V

- Dual Independent Current Limits

- 75mA to 1200mA

- ±10% Current Accuracy

- 20°C Temperature Band

- Reverse Current Blocking Protection

- Power Loop

- Low Quiescent Current

- 40µA Typical

- 1.0µA Max with Switch Off

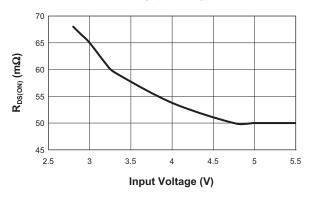

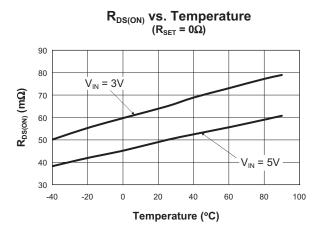

- 65m  $\Omega$  Typical  $R_{\text{DS(ON)}}$  at 3V

- Only 1.4V Needed for Enable Control Pin

- System READY Output with Externally Programmable Hysteresis

- Under-Voltage Lockout

- Temperature Range: -40 to 85°C

- 14-Pin TDFN33 Package

# **Applications**

- Capacitor Charger

- CF Card Port Power Protection

- Express Card GSM/GPRS/3G Modems

- PC Card GSM/GPRS Class 10/12 Modems

- WiMAX Cards

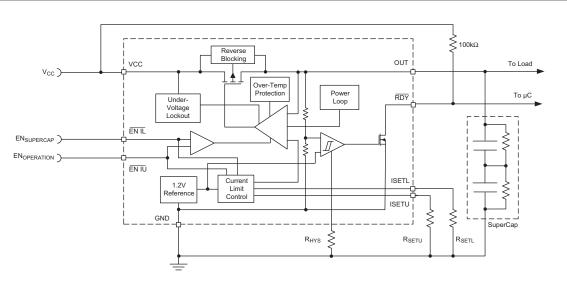

# **Typical Application**

# PC Card Current Limit Interface and Capacitor Charger

# **Pin Descriptions**

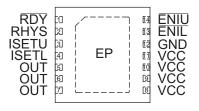

| Pin #        | Symbol                                                                                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                 |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1            | RDY                                                                                                                                                                                                                                                                                                   | System ready pin. Open drain, active low, initiated when the capacitor is 98% charged.                                                                                                                                                   |  |  |  |

| 2            | RHYS                                                                                                                                                                                                                                                                                                  | system READY hysteresis. Connect a resistor to ground to set the System Ready comparator hysteres                                                                                                                                        |  |  |  |

| 3            | ISETU                                                                                                                                                                                                                                                                                                 | Jpper current limit set input. A resistor from $I_{\mbox{\scriptsize SETL}}$ to ground sets the maximum upper current limit for he switch. Current limits can be set between 75mA and 1200mA. Connect to ground to disable current imit. |  |  |  |

| 4            | ISETL                                                                                                                                                                                                                                                                                                 | Lower current-limit set input. A resistor from $I_{SETU}$ to ground sets the maximum lower current limit for the switch. Current limit can be set between 75mA and 1200mA.                                                               |  |  |  |

| 5, 6, 7      | OUT                                                                                                                                                                                                                                                                                                   | P-channel MOSFET drain connection. Connect to super capacitor from OUT to GND.                                                                                                                                                           |  |  |  |

| 8, 9, 10, 11 | VCC                                                                                                                                                                                                                                                                                                   | Input pins to the P-channel MOSFET source. Connect 1µF capacitor from VCC to GND.                                                                                                                                                        |  |  |  |

| 12           | GND                                                                                                                                                                                                                                                                                                   | Device ground connection.                                                                                                                                                                                                                |  |  |  |

| 13           | EN ILEnable input. Active low enable with internal pull up. Also switches in the lower current limit initiating<br>the super capacitor to start charging.                                                                                                                                             |                                                                                                                                                                                                                                          |  |  |  |

| 14           | 14 EN IU Enable input. Active low enable with internal pull up. Also switches in the higher current limit to allow<br>System to start functioning. Can be directly connected to System Ready for automatic enabling. Whe<br>both EN IL B and EN IU B are enabled, I <sub>SETU</sub> will be selected. |                                                                                                                                                                                                                                          |  |  |  |

| EP           | EP                                                                                                                                                                                                                                                                                                    | The exposed thermal pad (EP) must be connected to the board ground plane and Pin 12. The ground plane should include a large exposed copper pad under the package for thermal dissipation (see package outline).                         |  |  |  |

# **Pin Configuration**

#### TDFN33-14 (Top View)

SmartSwitch™

PC Card Current Limit Interface and Capacitor Charger

# Absolute Maximum Ratings<sup>1</sup>

| Symbol                              | Description                       | Value                         | Units |

|-------------------------------------|-----------------------------------|-------------------------------|-------|

| V <sub>cc</sub>                     | VCC to GND                        | -0.3 to 6                     | V     |

| V <sub>EN</sub>                     | EN to GND                         | -0.3 to V <sub>cc</sub> + 0.3 | V     |

| V <sub>SET</sub> , V <sub>OUT</sub> | SET, OUT to GND                   | -0.3 to V <sub>cc</sub> + 0.3 | V     |

| I <sub>MAX</sub>                    | Maximum Continuous Switch Current | 2.5                           | A     |

## **Thermal Characteristics**

| Symbol          | Description                             | Value      | Units |

|-----------------|-----------------------------------------|------------|-------|

| θ <sub>JA</sub> | Maximum Thermal Resistance <sup>2</sup> | 50         | °C/W  |

| P <sub>D</sub>  | Maximum Power Dissipation <sup>2</sup>  | 2          | W     |

| T <sub>1</sub>  | Operating Junction Temperature Range    | -40 to 150 | °C    |

1. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

2. Mounted on an FR4 board.

PC Card Current Limit Interface and Capacitor Charger

# **Electrical Characteristics<sup>1</sup>**

$V_{CC}$  = 3.0V to 5.5V,  $T_A$  = -40°C to 85°C unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| Symbol                | Description                      | Conditions                                                                                                                                                                 | Min | Тур  | Max  | Units                 |  |

|-----------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-----------------------|--|

| V <sub>cc</sub>       | Operation Voltage                |                                                                                                                                                                            | 3.0 |      | 5.5  | V                     |  |

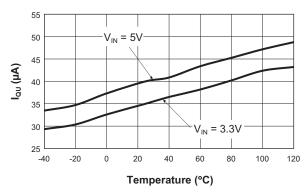

| I <sub>Q</sub>        | Quiescent Current                | $\overline{\text{EN IL}}$ or $\overline{\text{EN IU}} = V_{\text{CC}}$ , $I_{\text{OUT}} = 0$ , $R_{\text{HYS}} = 200 \text{k}\Omega$                                      |     | 40   | 75   | μA                    |  |

| I <sub>QU0</sub>      | Quiescent Current U <sub>0</sub> | $\label{eq:constraint} \begin{array}{ c c c c } \hline EN \ IL = V_{CC}, \ \overline{EN} \ IU = GND, \ I_{OUT} = 0, \ I_{SET} = GND, \\ R_{HYS} = 200 k\Omega \end{array}$ |     | 40   | 75   | μA                    |  |

| $I_{Q(OFF)}$          | Off Supply Current               | $\overline{\text{EN IL}} = \overline{\text{EN IU}} = V_{\text{CC}}$                                                                                                        |     | 0.4  | 1.0  | μA                    |  |

| $I_{SD(OFF)}$         | Off Switch Current               | $\overline{\text{EN IL}} = \overline{\text{EN IU}} = V_{\text{CC}}, V_{\text{SUPERCAP}} = 0$                                                                               |     | 0.4  | 10   | μA                    |  |

| V <sub>UVLO</sub>     | Under-Voltage Lockout            | Rising edge, 1% hysteresis                                                                                                                                                 |     | 2.7  | 3.0  | V                     |  |

| D                     | On-Resistance                    | $V_{CC}$ = 4.75V, $R_{SETL}$ = $R_{SETU}$ = 0k                                                                                                                             |     | 50   | 100  |                       |  |

| R <sub>DS(ON)</sub>   | OII-Resistance                   | $V_{CC} = 3.0V$ , $R_{SETL} = R_{SETU} = 0k$                                                                                                                               |     | 65   | 120  | mΩ                    |  |

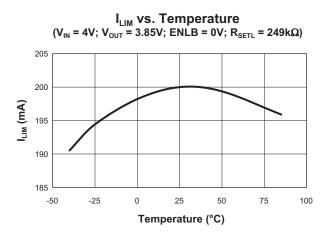

| т                     | Lower Current Limit Accuracy     | $R_{SETL} = 249k\Omega; \ \Delta T_A \le 20^{\circ}C$                                                                                                                      | 180 | 200  | 220  | mA                    |  |

| I <sub>LIMLACC</sub>  |                                  | $R_{SETL} = 249k\Omega$                                                                                                                                                    | 170 | 200  | 230  |                       |  |

| т                     |                                  | $R_{SETU} = 1.24 M\Omega; \Delta T_A \le 20^{\circ}C$                                                                                                                      | 900 | 1000 | 1100 |                       |  |

| I <sub>LIMUACC</sub>  | Upper Current Limit Accuracy     | $R_{SETU} = 1.24 M\Omega$                                                                                                                                                  | 850 | 1000 | 1150 | mA                    |  |

| $I_{LIM(MIN)}$        | Lower Minimum Current Limit      |                                                                                                                                                                            |     | 75   |      | mA                    |  |

| V <sub>EN(L)</sub>    | EN Input Low Voltage             | $V_{cc} = 3.0V$ to $5.5V^2$                                                                                                                                                |     |      | 0.4  | V                     |  |

| V <sub>EN(H)</sub>    | EN Input High Voltage            | $V_{cc} = 3.0V$ to $5.5V^2$                                                                                                                                                | 1.4 |      |      | V                     |  |

| $I_{EN(SINK)}$        | EN Input Leakage                 | $V_{EN} = 5.5V$                                                                                                                                                            |     |      | 1.0  | μA                    |  |

| T <sub>DEL(OFF)</sub> | Turn-Off Delay Time              | $V_{CC} = 5V$                                                                                                                                                              |     | 0.4  | 1.0  | μs                    |  |

| V <sub>RDY</sub>      | System READY Trip Threshold      | $V_{OUT}$ rising, $T_A = 25^{\circ}C$                                                                                                                                      |     | 98   |      | % of $V_{\text{OUT}}$ |  |

| V <sub>RDYHYS</sub>   | System READY Hysteresis          | $R_{HYS} = 200 k\Omega$                                                                                                                                                    |     | 200  |      | mV                    |  |

| V <sub>RDY(L)</sub>   | System READY Voltage Low         | $I_{SINK} = 1 mA$                                                                                                                                                          |     |      | 0.4  | V                     |  |

| $I_{RDY}$             | RDY Leakage Current              | $V_{RDY}$ < 5.5V, $V_{OUT}$ < 98% of $V_{OUT}$                                                                                                                             |     |      | 1.0  | μA                    |  |

| OTMP                  | Shutdown Temperature             |                                                                                                                                                                            |     | 145  |      | °C                    |  |

<sup>1.</sup> The AAT4621 is guaranteed to meet performance specification over the -40°C to 85°C operating temperature range and is assured by design, characterization and correlation with statistical process controls.

<sup>2.</sup> For  $V_{\ensuremath{\text{IN}}}$  outside this range consult the Typical EN Threshold curve.

SmartSwitch™

PC Card Current Limit Interface and Capacitor Charger

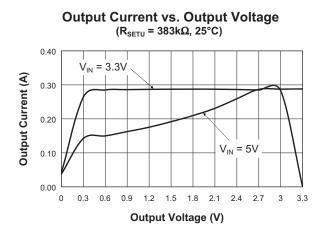

# **Typical Characteristics**

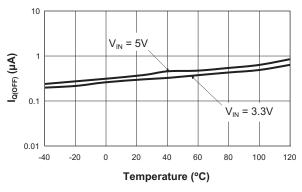

Reverse Off-Switch Current vs. Temperature (E<sub>NUB</sub> = E<sub>NLB</sub> = V<sub>CC</sub>; V<sub>IN</sub> = 0V)

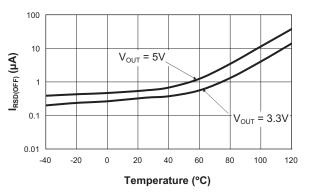

Off-Switch Current vs. Temperature  $(E_{NUB} = E_{NLB} = V_{CC}; V_{OUT} = 0V)$

$\begin{array}{c} R_{\text{DS(ON)}} \text{ vs. Input Voltage} \\ (R_{\text{SET}} = 0 k \Omega) \end{array}$

SmartSwitch™

PC Card Current Limit Interface and Capacitor Charger

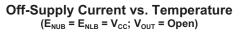

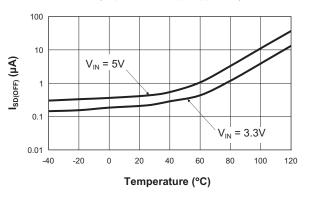

# **Typical Characteristics**

$\begin{array}{l} \textbf{Quiescent Current } I_{\text{QU}} \text{ vs. Temperature} \\ (E_{\text{NUB}} = 0V; E_{\text{NLB}} = V_{\text{CC}}; \text{ or } E_{\text{NLB}} = 0V; E_{\text{NUB}} = V_{\text{CC}}; V_{\text{OUT}} = \text{Open}) \end{array}$

$I_{LIM}$  vs. Temperature (V<sub>IN</sub> = 4V; V<sub>OUT</sub> = 3.85V; ENUB = 0V; R<sub>SETU</sub> = 1.3MΩ) 1020 1010 1000 I<sub>LIM</sub> (mA) 990 980 970 960 950 -50 -25 0 25 50 75 100 Temperature (°C)

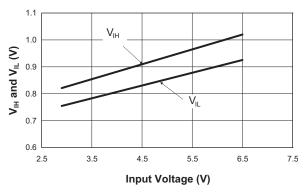

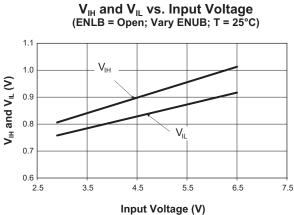

V<sub>IH</sub> and V<sub>IL</sub> vs. Input Voltage (ENUB = Open; Vary ENLB; T = 25°C)

Α

AT4621

PC Card Current Limit Interface and Capacitor Charger

# **Typical Characteristics**

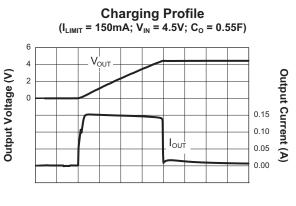

Time (20ms/div)

Time (20ms/div)

Time (2ms/div)

Time (2ms/div)

Time (5s/div)

SmartSwitch™

PC Card Current Limit Interface and Capacitor Charger

# **Typical Characteristics**

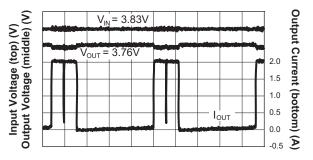

Time (1s/div)

# $\begin{array}{c} \textbf{GSM900 GPRS Class 12 Transmit}\\ \textbf{1-Slot Ch975, 33dBm} \end{array} \\ \textbf{(n)} \textbf{(n$

**PRODUCT DATASHEET**

**AAT4621**

Time (1ms/div)

#### GSM900 GPRS Class 12 Transmit 2-Slot Ch975, 33dBm

Time (1ms/div)

PC Card Current Limit Interface and Capacitor Charger

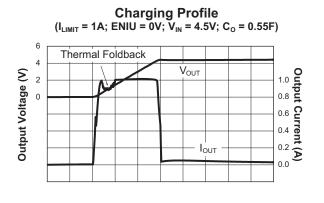

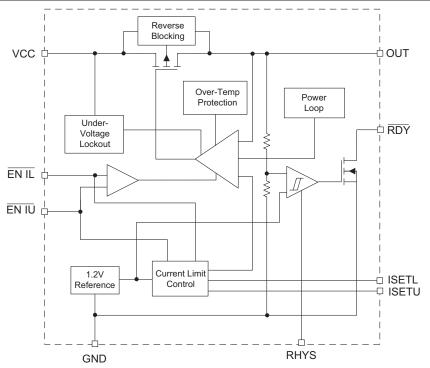

# **Functional Block Diagram**

## **Functional Description**

The AAT4621 is an integrated P-channel MOSFET load switch with an upper and lower adjustable current limits which can be enabled independently, over temperature protection, a power loop and a super capacitor charger. The current limit control is combined with an over temperature thermal limit and power loop circuit to provide a comprehensive system to protect the load switch and its supply from load conditions which exceed the supply specifications. The AAT4621 has been designed specifically to provide the interface between a PCMCIA host and PC card where a super capacitor has been used to "average out" high pulse currents which would otherwise exceed the PCMCIA/ Express Card power specifications. e.g. GSM/ GPRS modem cards, where pulse currents during transmit signals can exceed the 1A maximum specification (1.3A in the case of Express Card).

The current limit and over temperature circuits act independently. The device current limit is activated when the output load current exceeds an internal threshold level. There are two internal current limits which are enabled independently. The current limit threshold in each case is determined by external resistors connected between the two SET pins and ground. The minimum current limit threshold is specified by  $I_{\text{LIM}(\text{MIN})}$ . If the load condition maintains the device in current limit and the chip temperature reaches a critical point, then an internal power loop will reduce the current to a safe level. Connecting ISETU to ground disables the current limit protection allowing a low impedance path to the host  $V_{\text{CC}}$ .

The load switch is turned off by applying a logic high level to both of the EN pins. When both  $\overline{\text{EN IL}}$  and  $\overline{\text{EN IU}}$ are selected ISETU will be selected. The EN function has logic level thresholds that allow the AAT4621 to be TTL compatible and may also be controlled by 2.5V to 5.0V CMOS circuits. The voltage level applied to the EN pins should not exceed the input supply level present on the VCC pin. The AAT4621 typically consumes 40µA when operating, when off, the device draws less then 1µA. In the off state, current is prevented from flowing between the input and output.

Under-voltage lockout circuitry ensures that the V<sub>cc</sub> supply is high enough for correct operation of the IC. Also included is a System Ready function which will be activated when the capacitor voltage is charged and the load is permitted to take current. For automatic functionality, this pin can be directly connected to the  $\overline{\text{EN IU}}$  pin. An external resistor is provided to add hysteresis to this function.

SmartSwitch™

PC Card Current Limit Interface and Capacitor Charger

# **Application Information**

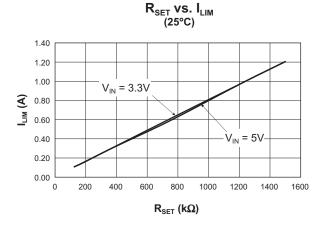

## **ISETU and ISETL Current Limit Set**

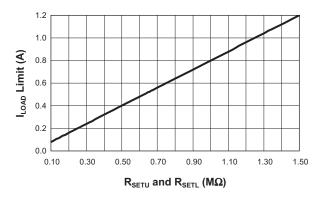

The AAT4621 current limit is set at two different levels. Resistors from ISETL and ISETU set the lower and upper current limit levels respectively.

The ISETL and ISETU nodes operate within a window of 0.75V to 1.5V for resistor values ranging from 93.75 $\Omega$  to 1.5M $\Omega$ . Resistor values outside this range are not recommended. The ISETL and ISETU source current varies with the resistor value used according to Table 1. To determine the resulting current limit multiply the R\_{SETU} or R\_{SETL} node voltage times the gain in Table 1. Note that the voltage at the node varies from 0.75V to 1.5V and the current limit gain varies depending on the resistor value used.

$$V_{ISET} = R_{SET} \cdot I_{ISET} = 0.75V$$

to 1.5V

If the set pin is open circuit or allowed to exceed 2V, all power devices are disabled and the input is disconnected from the output. Shorting the set pin to GND enables all power devices and shorts the  $V_{CC}$  to the output pin with no current limit.

To activate the upper current level ( $R_{SETU}$ ) pull  $\overline{EN IU}$  low. To activate the lower current level ( $R_{SETL}$ ) pull  $\overline{EN IL}$  low. If both  $\overline{EN IU}$  and  $\overline{EN IL}$  are pulled low the  $\overline{EN IU}$  current limit level ( $R_{SETU}$ ) will be selected.

Figure 1: Calculated Current Limit R<sub>SET</sub> Characteristic.

| R <sub>set</sub> Range | Ι <sub>ISET</sub><br>(μΑ) | I <sub>LIM</sub> /<br>V <sub>ISET</sub><br>(A/V) | Current<br>Limit<br>Range<br>(A) | Current<br>Limit                         |

|------------------------|---------------------------|--------------------------------------------------|----------------------------------|------------------------------------------|

| 1.5Meg-750k            | 1                         | 0.8                                              | 1.2-0.6                          | $R_{\text{SET}} \cdot 1 \mu A \cdot 0.8$ |

| 750k-375k              | 2                         | 0.4                                              | 0.6-0.3                          | $R_{\text{SET}} \cdot 2\mu A \cdot 0.4$  |

| 375k-187.5k            | 4                         | 0.2                                              | 0.3-0.15                         | $R_{\text{SET}} \cdot 4 \mu A \cdot 0.2$ |

| 187.5-93.75k           | 8                         | 0.1                                              | 0.15-0.075                       | $R_{\text{SET}} \cdot 8 \mu A \cdot 0.1$ |

Table 1: R<sub>SET</sub> Table.

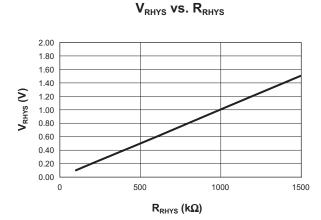

## System Ready Hysteresis (RHYS) and System Ready (RDY)

In internal comparator senses the output voltage and delivers a ready signal to the external micro controller when the output voltage reaches 98% of the final value ( $V_{CC}$ ). The comparator hysteresis is programmed by a resistor from the RHYS pin to ground. The RHYS voltage determines the hysteresis voltage and is equal to the RHYS source current (1µA) times the RHYS resistance.

$$V_{HYST} = R_{HYS} \cdot 1\mu A$$

$$= 200k\Omega \cdot 1\mu A$$

$$= 0.2V$$

The system ready pin ( $\overline{\text{RDY}}$ ) is an open drain output that switches low when the output voltage reaches 98% of the input voltage. It requires an external pull up resistor tied to the input voltage with a typical value of  $100 \text{k}\Omega$ .

### **Power Loop**

The AAT4621 power loop limits the load current in the event that the device power dissipation becomes excessive. The AAT4621 power loop regulates the die temperature to 110°C, decreasing the load current in increments of 1/32 of the current limit set point when the die temperature reaches 110°C. When the die temperature exceeds 110°C it decreases the load current by 1/32 of the current limit set point. If die temperature is less than 110°C, it increases the load current in increments of 1/32 of the current limit set point until the set current limit point is reached or the die temperature exceeds 110°C.

The delay time between die temperature measurements varies depending on the load current limit set point. The delay ranges from 0.5ms for a 75mA current limit set point to 4ms for a 1.2A current limit set point.

SmartSwitch™

## PC Card Current Limit Interface and Capacitor Charger

For the condition where there is no current limit set point (shorting  $R_{SETU}$  or  $R_{SETL}$  to ground) the soft start increments the current limit is 1/32 steps of 1.2A until the current reaches 1.2A, at which point the power MOSFET turns on fully. At this point, the current is limited by the  $R_{DS(ON)}$  of the power MOSFET and other series resistance. The Power Loop and Over-Temperature Loop then takes control to limit the current until the output voltage has fully charged.

### **Over-Temperature Protection**

If the die temperature rate of rise is fast enough to exceed the power loop regulated temperature, overtemperature shutdown disables the device. The overtemperature threshold is 145°C. After over-temperature shutdown, soft start is initiated once the die temperature drops to 130°C.

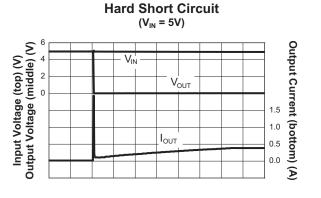

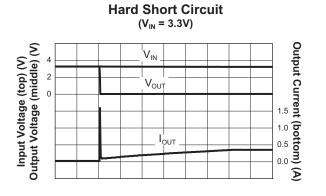

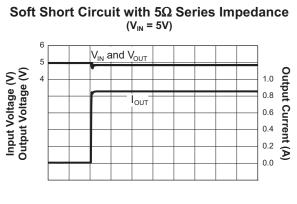

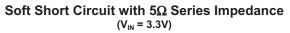

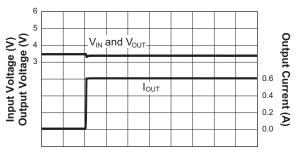

## **Short Circuit Protection**

The series pass power MOSFET turns off completely after the output has charged to within 18mV of the input voltage. This protects the device in the event where a short circuit is applied to the output. After applying a short circuit or heavy load to the output, which causes the output to sink below the 18mV threshold plus some hysteresis, the current will immediately attempt to slew from zero to the final programmed value. The device will continue to output the current limit as long as the output is V<sub>IN</sub> - 18mV or until the die temperature reaches 110°C. If temperature foldback occurs, then the power loop will become active.

### **Under-Voltage Shutdown**

Under-voltage lockout enables the device at 2.7V typical with 100mV of hysteresis. The maximum UVLO level is 3.0V.

#### Digitally Programmed Soft Start Current Limit

At turn on, the digital soft start increases the load current in discrete levels equal to 1/32 of the final programmed current limit set point from zero to the final programmed current limit level. Once the AAT4621 has fully charged the supercap, the soft start circuit is disabled. The soft start function will only reactivate under the following conditions:

- 1. The power source or enable is cycled off and back on.

- 2. The thermal shutdown is activated

- 3. Switching from ENU to ENL or vice versa or

- 4. Following an over-current event, e.g. a hard output short circuit.

#### **Reverse Current Blocking**

An internal comparator disables the internal pass transistor when the input voltage is less than the output voltage blocking any reverse current from the output to the input.

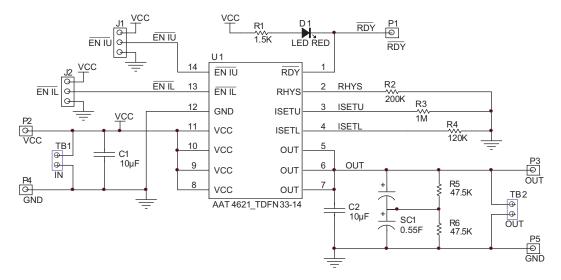

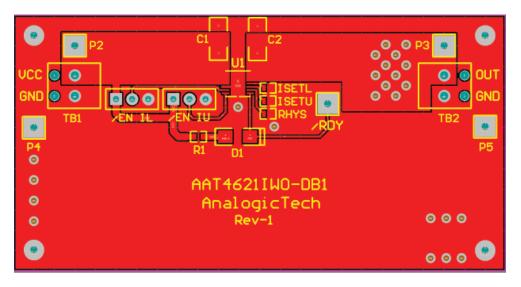

## **Evaluation Board**

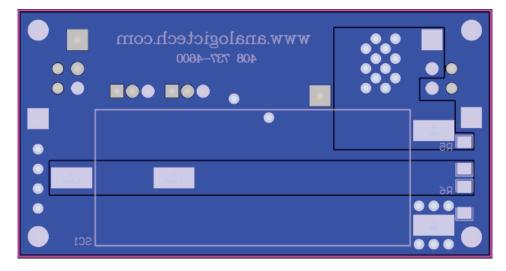

The AAT4621 evaluation board schematic is shown in Figure 2. The AAT4621 PCB layout is shown in Figures 3 and 4.

#### Layout Guidance

When laying out the PC board, the following layout guideline should be followed to ensure proper operation of the AAT4621:

- 1. The exposed pad EP must be reliably soldered to GND. The exposed thermal pad should be connected to the board ground plane and Pin 12. The ground plane should include a large exposed copper pad under the package with VIAs to all board layers for thermal dissipation.

- 2. The power traces, including GND traces and the VIN trace should be kept short, direct and wide to allow large current flow. Use several via pads when routing between layers.

- The input capacitors (C1) should be connected as close as possible to VCC (Pins 8, 9, 10, 11) and GND (Pin 12) to get good power filtering.

- 4. The output capacitor (C2) should be connected as close as possible to OUT (Pins 5, 6, 7) and GND (Pin 12) to get good power filtering as the device will recharge the Supercap when the output voltage level sensed on the OUT pin is reduced by approximately 18-20mV below its input voltage (VCC) level.

PC Card Current Limit Interface and Capacitor Charger

Figure 2: AAT4621 Evaluation Board Schematic.

Figure 3: AAT4621 Evaluation Board PCB Top Side.

SmartSwitch™

PC Card Current Limit Interface and Capacitor Charger

Figure 4: AAT4621 Evaluation Board PCB Bottom Side.

## PC Card Current Limit Interface and Capacitor Charger

# **Ordering Information**

| Package   | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------------------|------------------------------------------|

| TDFN33-14 | YWXYY                | AAT4621IWO-T1                            |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/about/quality.aspx.

# Package Information<sup>3</sup>

All dimensions in millimeters.

1. XYY = assembly and date code.

- 2. Sample stock is generally held on part numbers listed in **BOLD**.

- 3. The leadless package family, which includes QFN, TQFN, DFN, TDFN and STDFN, has exposed copper (unplated) at the end of the lead terminals due to the manufacturing process. A solder fillet at the exposed copper edge cannot be guaranteed and is not required to ensure a proper bottom solder connection.

PC Card Current Limit Interface and Capacitor Charger

Advanced Analogic Technologies, Inc. 3230 Scott Boulevard, Santa Clara, CA 95054 Phone (408) 737-4600 Fax (408) 737-4611

© Advanced Analogic Technologies, Inc.

© Advanced Analogic Technologies, Inc. AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in AnalogicTech's terms and conditions of sale, AnalogicTech assumes no liability whatsoever, and AnalogicTech disclaims any express or implied warranty relating to the sale and/or use of AnalogicTech products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed. AnalogicTech logo are trademarks of Advanced Analogic Technologies Incorporated. All other hard and enduct appression provided by the customer to minimize interpact or the hidder. brand and product names appearing in this document are registered trademarks or trademarks of their respective holders.